錦です。

NVIDIAは、昨夜開催されたGTCの基調講演で「Grace」CPUの詳細を少しだけあきらかにしました。

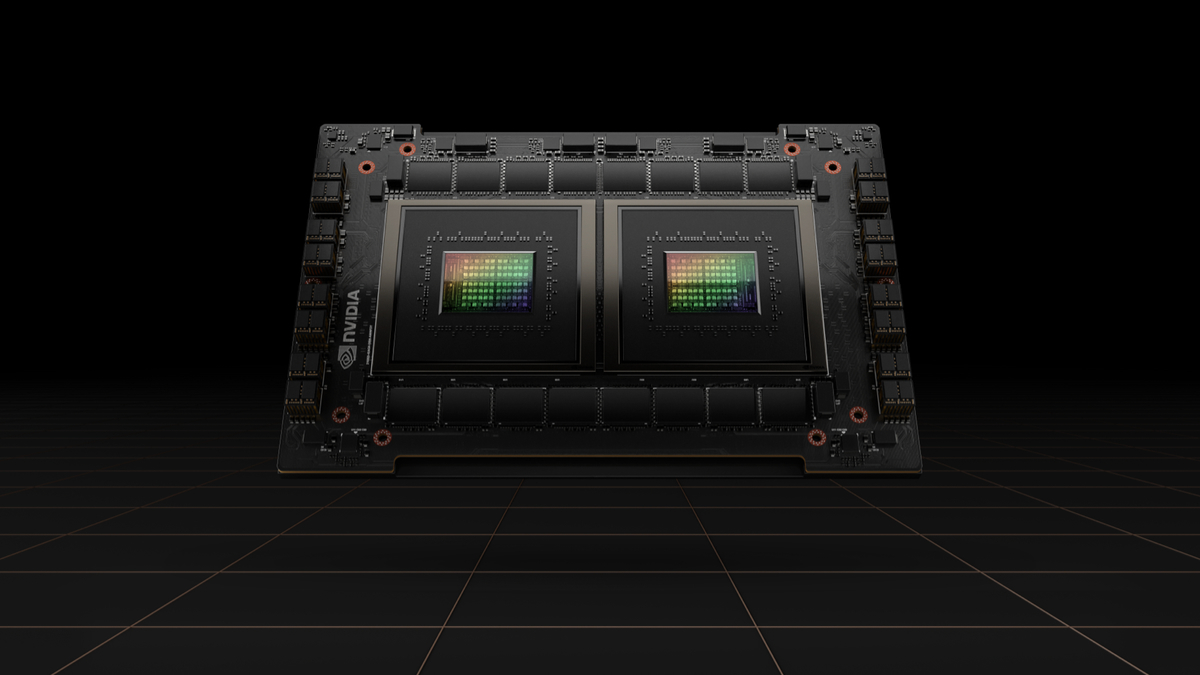

Hopper

Hopperについては以下の記事を御覧ください。

Grace

「Grace」は、ArmをベースにしたCPUです。今回明らかになったのは、その部分的な仕様です。

まず既にわかっている内容からまとめます。

NVIDIA初のデータセンター向けのCPU「Grace」が発表 ~ Armを採用・900GB/sの転送速度を実現 - Nishiki-Hub

明らかになった仕様と性能

さて、では今回新たにあきらかになったものを紹介していきます。

まず、CPUのコア数から。CPUのコア数は144コアになりました。他のArmプロセッサとちがってbig.LITTLEを採用しているという情報もなく、Neoverse以外のアーキテクチャも発表されていませんのでほぼ確実に全コアNeoverseでしょう。また、CPUっ自体はスケーラブルなものになっており、マルチソケットに対応。後で話しますが、2基のGraceを搭載するシステムも構成可能です。

そして、命令セットは最新のArmv9に対応。Armのシングルスレッド性能と新世代のベクトル拡張セットのサポートを、NVIDIAのシステムと組み合わせることによって、Graceは、多くのアプリケーションに即時のメリットをもたらすとのこと。

肝心の性能ですが、SPECrate 2017 int_baseベンチマークでは他社をぶっちぎる推定740のパフォーマンスになるとしています。AmpereベースのDGX A100では、AMDのZen 2「Rome」のデュアルソケットでしたが、Graceはその1.5倍の性能になります。

メモリ

統合されるメモリは、LPDDR5XでECCに対応。メモリ帯域は、1TB/sとDDR5の2倍となっています。また、ArmベースのCPUとLPDDR5xを組み合わせることによって144コアという超大規模プロセッサでありながら500Wという低電力・高効率を実現しています。オンチップのキャッシュは396MB。

ソフト

ソフトとしてGraceはNVIDIAのすべてのソフトウェアがGraceに対応します。NVIDIAのソフトウェアとは、RTX、HPC、AI、Omniverseなどを筆頭とした高機能アプリケーション集団です。

Grace-Hopper

NVIDIAはGPUの開発コードネームに、故人の数学者の名前を当てはめています。今回発表された「Grace」も、同時に発表された「Hopper」もともに、同じ人物、Grace Hopper氏に由来しています。Hopper氏はプログラミング言語COBOLを開発した、世界で最初のプログラマの一人と言われています。

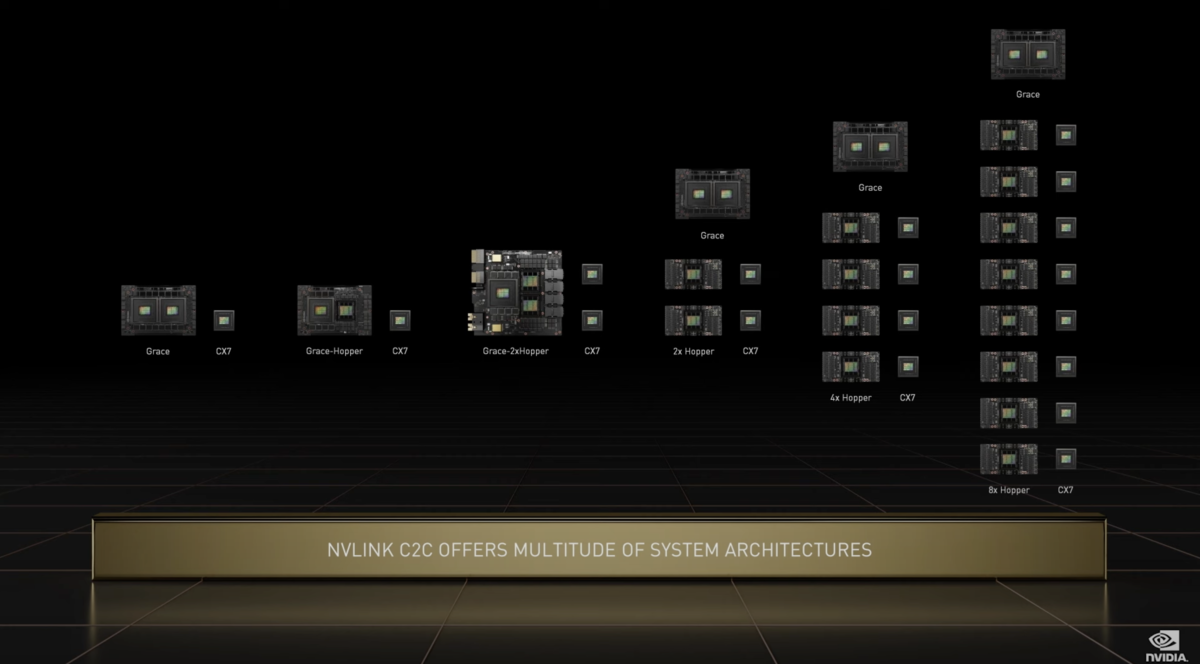

今回、NVIDIAが同人物からCPUとGPUの名前を採っているということはすなわちセットで使うことを前提としています。

まず、NVIDIAのGraceとHopperにはワンペアあたり1基の「CX-7 SmartNIC」が搭載されます。CX-7は、CPUやdRAMを介さないネットワークをGPUに直接接続できるインターフェイスです。チップセットのようなものだと考えればいいのでしょうか。

Grace Hopper間の接続には第4世代NVLinkが用いられます。この帯域は既に発表されているとおり900GB/sでの通信です。

また、NVLinkで統合されるのは、Grace Hopperだけでなく、将来的にはCPU・GPU・NIC・DPU・SOCなどのNVIDIAチップに広がります。しかもそこに、顧客のIPも組み合わせることが可能になります。この組み合わせというのは、オンダイでも可能になるとのことで、極端な例を挙げると、IntelのCPUとNVIDIAのGPU/CPUがオンダイで統合することも可能であるということを意味しています。