錦です。

NVIDIAは先程GTC 2022の基調講演を開催し、Ampereアーキテクチャの後継となる「Hopper」アーキテクチャと、Hopperの最上位となるであろうGPU「NVIDIA H100」、そしてH100を採用した「DGX H100」システムを発表しました。

NVIDIA H100

「NVIDIA H100」は、新しいGPUアーキテクチャ「Hopper」を採用した研究など向けのGPUです。

現時点で、Hopperアーキテクチャ自体が、Ampere世代のようにゲーミング向けにも展開されるのか、あるいは研究向け(旧Teslaブランド)の展開にとどまるのかはまだ明らかになっていません(リーク話も加えるとAda Lovelaceというアーキテクチャが並行して発表を持っている)。

Hopperアーキテクチャとして基調講演で明らかになった内容というのは少なく、GTCの期間中にあきらかになるそう。これはH100の仕様もあきらかになっていないということで、この記事では基調講演で発表された内容を中心にお届けします。

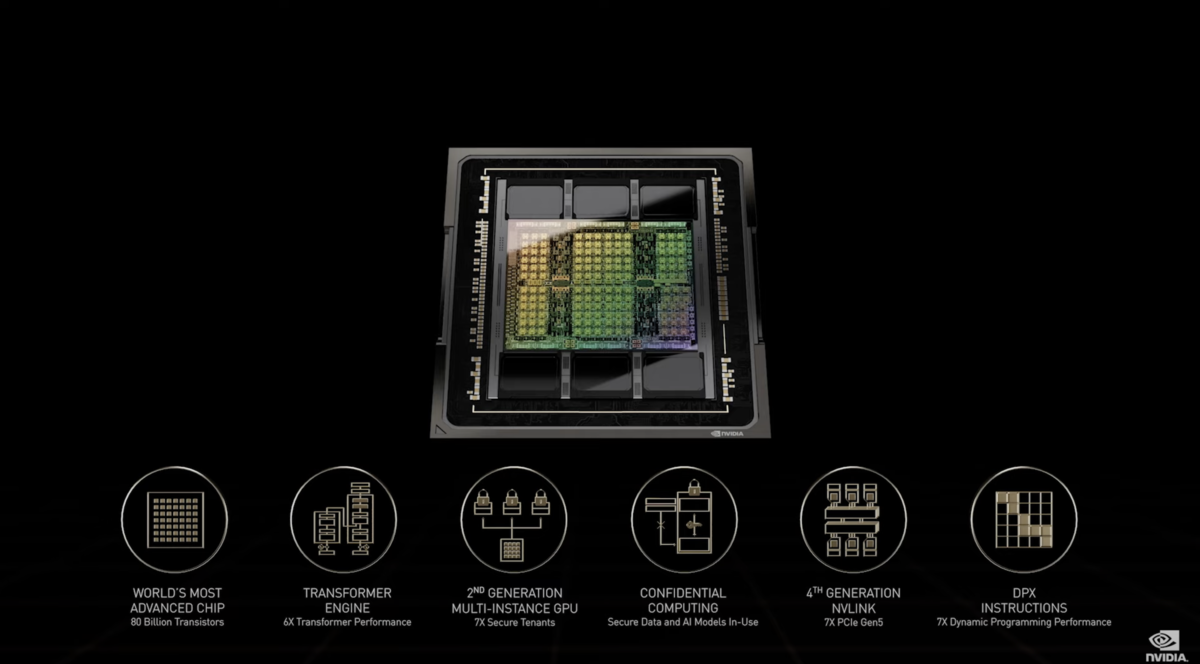

まず、大雑把なハードウェアの仕様ですが、TSMC N4(4nm)で製造されており、800億のトランジスタを搭載しています。前世代のA100が、TSMC N7での製造かつトランジスタの数は500億となっているので、順当な進化と言えます。帯域は、4.9TB/s。

ただし、今回は機能に注目すべきです。

こちらは、H100の主要な特徴がまとめられたものです。左から2番目から紹介します。

「Transformer」とは自然言語処理に活用される深層学習のモデルです。現在では、多くの翻訳機能や手書き認識などに用いられるモデルです。H100ではTensorコアが、このTransformerのためのエンジン「Transformer Engine」に強化されており、前世代よりTranceformerにおいての性能が6倍高速になります。性能については後述の項目を参照のこと。

そして3番目、「第2世代マルチインスタンス」。これは、H100を複数のインスタンスに分ける事ができるというものです。AmpereのA100にもありました。分けられるインスタンスの最大数は7で、これはA100と変わりません。インスタンスには一つ分のGPCとvRAMが含まれています。前世代からの進化としては、インスタンスを完全に分離できるようになったことや、IO仮想化の追加、クラウドでのマルチテナンシーに対応します。また、デコーダ(NVDEC)とJPEGデコーダが新たにこれに含まれています。

ちなみに、クラウンドテナンシーはAmpereでは最大1基でしたが、Hopperでは7基になります。そしてこのそれぞれが、2基のT4 GPUと同じ推論性能を持ちます。

そして、飛ばして6番目、DPX命令の追加。これがDynamic Programing:動的計画法というものの機能の追加です。

動的計画法とは、計算機科学の分野においてのアルゴリズムの分類の一つです。超簡単に言うと、一回求めだした答えを再利用して、別の答えを導くというものです。

ex:)1+1を求めて2を出した後、1+1+3という式に出くわしたら前述の2を使って2+3と計算するというアルゴリズムです。

DPX命令はこの動的計画法を高速化するための命令で、この命令を用いると7倍高速に処理することができるそうです。この高速化によって、多くのアルゴリズム処理で高速化が図られる様になるとしています。

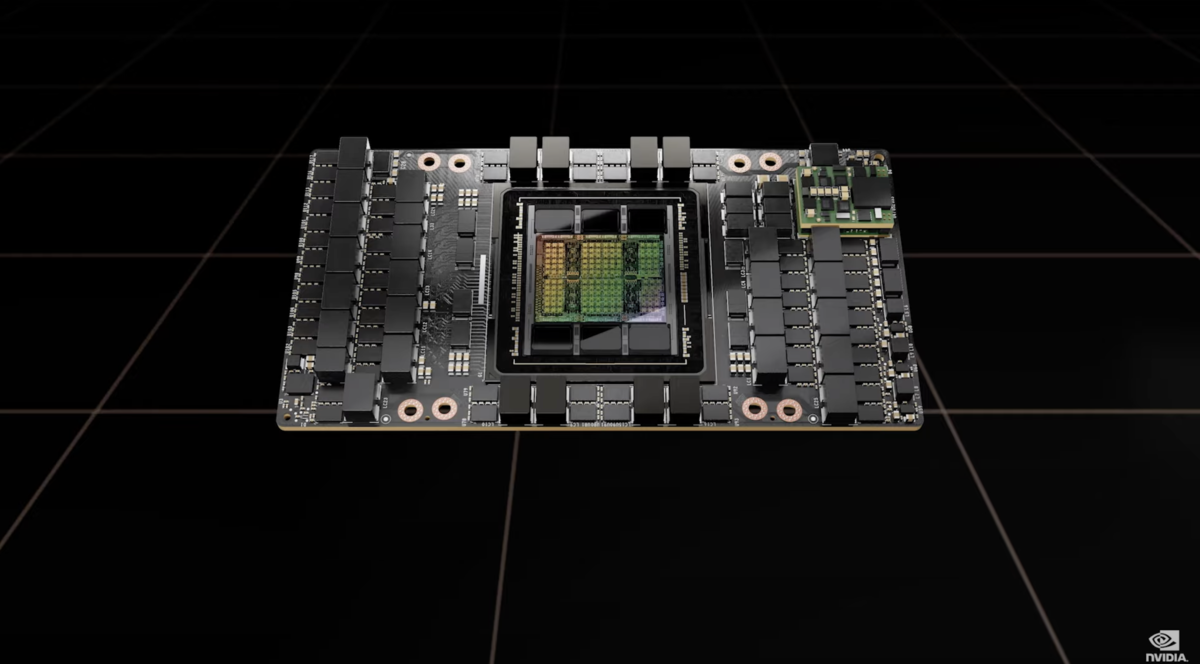

メモリと基盤

メモリは、80GBのHBM3メモリをTSMCの「CoWoS」という2.5Dパッケージを使ってパッケージされており、電圧制御とSXMというスーパーチップモジュールに統合されています。

メモリ帯域は3TB/s(PCIeモデルが2TB/s)と非常に広い帯域になっています。

そして、GPU間の通信ですが、NVLink仕様時は900GB/s、PCIe仕様時は128GB/sになります。PCIeはGen 5に対応します。

また、SXMシステムのTDPは700Wとなっています。

単体での性能

単体での性能をまとめます。

| SXM | PCIe | |

|---|---|---|

| FP64 | 30 TFLOPS | 24 TFLOPS |

| FP 64 Tensorコア | 60 TFLOPS | 48 TFLOPS |

| FP32 | 60 TFLOPS | 48 TFLOPS |

| TF 32 Tensorコア | 1000 TFLOPS | 800 TFLOPS |

| Bfloat16 Tensorコア | 2000 TFLOPS | 1600 TLOPS |

| FP16 Tensorコア | 2000 TFLOPS | 1600 TLOPS |

| FP8 Tensorコア | 4000 TFLOPS | 3200 TFLOPS |

| INT8 Tensorコア | 4000 TOPS | 3200 TOPS |

こちらの性能は、スパース性をりようした性能を示しています。

1000 TeraFLOPS = 1 PetaFLOPSなので、Tensorコアではテラを超えたペタの性能を持っているということになります。前世代との性能差は、FP8性能が6倍、FP16、TF32、FP64では3倍高速化します(ただし、TensorコアあるいはTranceformer Engineを利用した場合)。

えぐい。

なお、CUDAコアの数などの仕様はまだ明らかになっていません。

DGX H100

そして、H100 GPUを採用したシステムが「DGX H100」です。

DGX H100には8基のH100のSXMシステムが搭載され、こちらも前世代の「DGX A100」と比較して、FP8性能が6倍の32 PFLOPS、FP64では3倍の5000 TFLOPSに高速化します。

今回、搭載CPUはあきらかになっていませんが、まだGraceが出荷段階にない(来年出荷)とアナウンスされているので、順当に考えれば前世代同様、AMDのEPYCが採用されているとみられます(Milanベースになるのかな)。

今回の目玉

また、同時にDGX H100を32台、H100を計256基接続した「NVIDIA DGX SuperPOD with DGX H100」が発表されており、コチラはFP8で1 EFLOPS(=1000 PFLOPS)の性能を持ちます。で、このSuperPODを18基接続した「Eos」というスパコンもお披露目されました。

Eosは18 EFLOPSのFP8性能を持ち、AI性能は現在世界最速のスパコンである日本の「富岳」を4倍も上回るとしています。

登場時期

H100 GPUの登場時期は、今年第3四半期からの出荷開始となっています。