Armは新世代のCPUアーキテクチャとして、「Neoverse V3」「Neoverse N3」「Neoverse E3」とそれぞれのCompute Subsystem(CSS)を発表しました。

新IP

今回登場したあたらしいIPはすべてArmv9-A(v9,2)ISAに基づいており、これにはベクトル演算の拡張命令セットであるSVE2を搭載しています。ベクトル演算が高速になるという関係で、AI性能が大幅に向上しています。

また、UCIe 1.1のサポートなどの共通した変更点もあります。詳しくそれぞれのIPについて見ていきましょう。

Neoverse V3

Neoverse Vシリーズは、主にHPCで用いられるアーキテクチャです。主な採用例としては、AWSの「Graviton4」やNVIDIAの「Grace」にも採用されています。

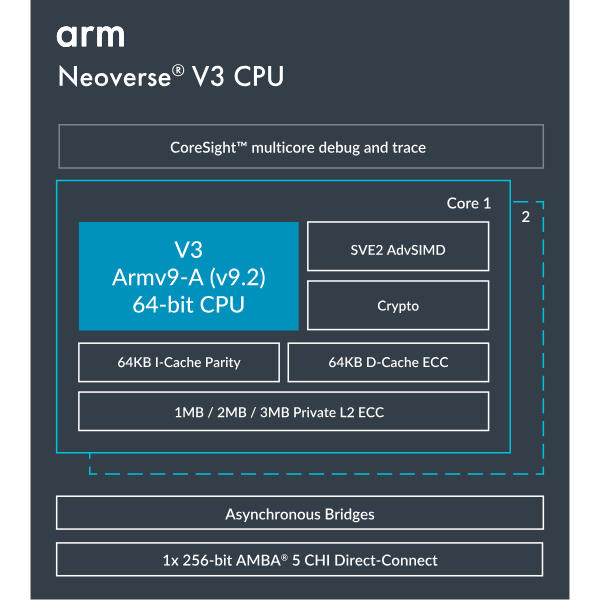

Neoverse V3はその第3世代となっており、Armv9-A(v9,2)命令セットをベースにしており、SVE2 SIMD拡張命令などに対応しています。

コアあたりのキャッシュは、命令キャッシュとデータキャッシュがそれぞれ64KB、L2キャッシュが1MB/2MB/3MBでECC対応となっています。

Armによると、一般的なサーバーワークロードのシミュレーションにおいて、32コアNeoverse V2と比較して9%~16%の性能向上を実現しており、AIデータ分析においては、V2と比較して84%の性能向上を実現しているとのことです。

そして、Neoverse V3をベースに展開されたCSSでは、64コアのNeoverse V3に、12チャネルのDDR5/LPDDR5/HBMのサポートが含まれています。その他、64レーンのPCIe Gen 5や、ダイツーダイ相互接続、UCIe 1.1などをサポートしています。

ソケットあたり、最大128コアまでのNeoverse V3を拡張することができ、HPCへの応用が期待されています。

Neoverse N3

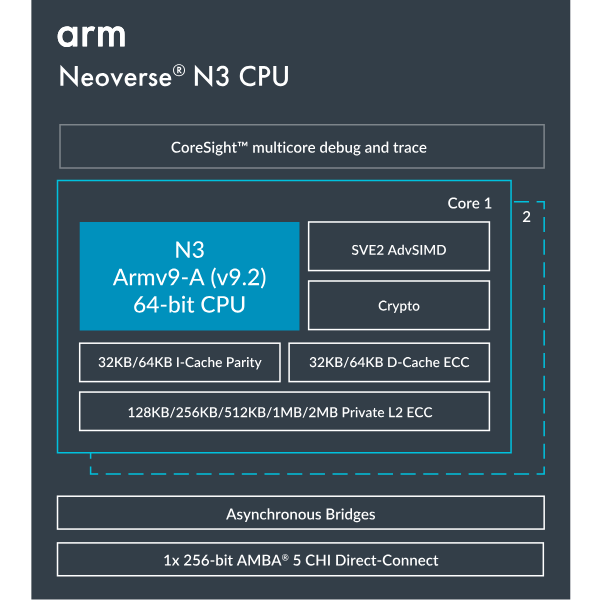

Neoverse N3は、パフォーマンスと消費電力のバランスを提供する必要がある汎用CPU向けあるいはインフラ向けのIPです。V3同様にArmv9-Aに基づいています。

コアあたり32KBあるいは64KBの命令キャッシュ及びデータキャッシュのL1キャッシュと、128KB~2MBのECC対応L2キャッシュを搭載しています。

32コアのNeoverse N3は、32コアNeoverse N2と比較して、ビデオ処理で9%、SQLで30%、整数演算性能が11%、Python実行が13%、NoSQL KVcacheで13%、圧縮で22%、AIデータ分析で最大196%の性能向上を実現しています。

Neoverse N3をベースとしたCSSは、32コアのNeoverse N3を搭載しており、4チャネルのDDR5あるいはLPDDR5、CXLのサポート、UCIe 1.1のサポートなどが含まれています。現在のNeoverse N2 CSSがMicrosoftのCobalt 100に採用されているため、今後登場する可能性があるCobalt 200(仮称)にはこのCSSが採用される可能性がありますね。

Neoverse E3

Neoverse E3については現時点で詳細な情報が確認されていませんので、詳細は追って掲載します。