錦です。

Intelは、第12世代Core「Alder Lake」について、同社のイベント「Intel Architecture Day 2021」で発表しました。

Alder Lakeに採用されるCPUコア

Alder Lakeに採用されるコアは2つに分かれており「効率コア(Efficient Core)」と「性能コア(Performance Core)」に分かれています。これらを組み合わせて、Armのように役割分担のような形でプロセッサを構成します。

Intelはこれを「Intel Hybrid Technology」と名付けており、Sunny Cove+Tremontの構成を持つLakefieldが先行して投入されています。この技術を採用することによって、高性能かつ高効率で、消費電力の抑制につなげています。

Intelのアーキテクト、Raja Koduri氏はこのIntel Hybrid Technologyについて、長い時間バッテリーが持つ上、パフォーマンスも向上すると述べています。

ではまず、効率コアに当たる「Gracemont」から見ていきましょう。

Gracemont

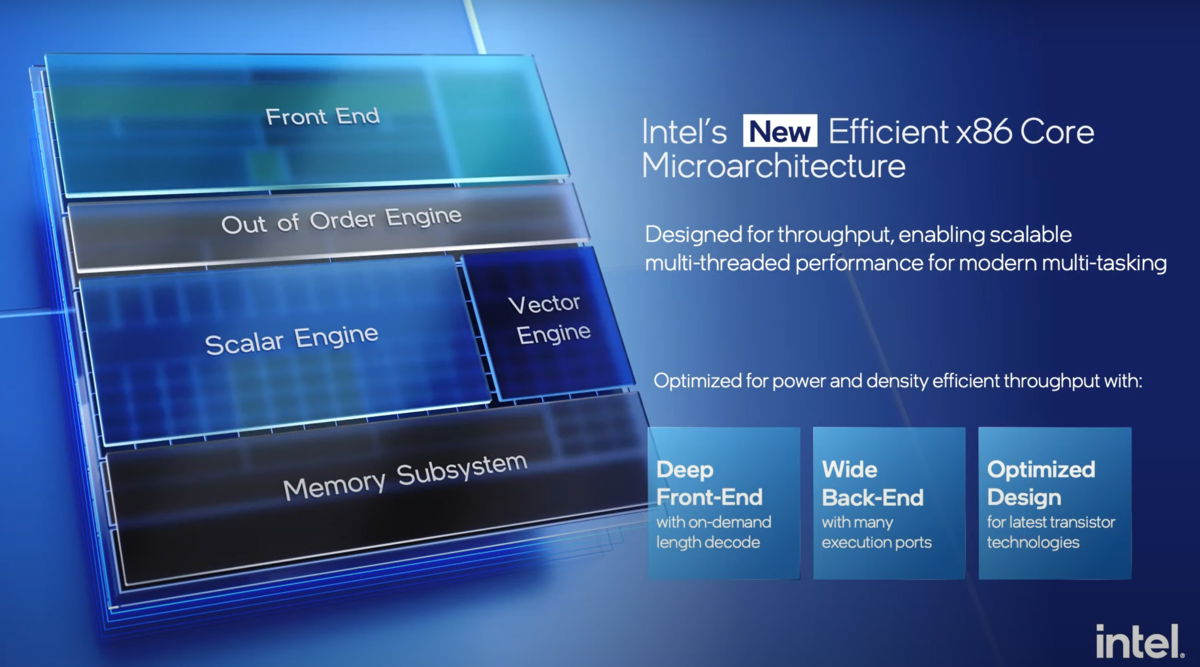

効率コアは、Atomの流れを汲むアーキテクチャ「mont」系統のコアが採用されます。今回採用されるのは「Gracemont」というアーキテクチャ。Intel曰く、「史上最高に高効率なx86プロセッサ」であるとのこと。最新のマルチタスクキングに対応したスケーラブルなマルチスレッドパフォーマンスを実現するとしています。

具体的には、コアあたりで、Skylakeからみて40%電力効率が高いとのことです。また、Skylakeの2C4TのCPUに対して、Gracemontの4C4TのCPUは同じくロックで80%高い性能を実現するか、同じ性能で80%省電力で動作します。なんか、Appleも高効率コアだけでIntel MacBook Airと~~~と高効率コアの高性能さをアピールしてましたが、やっぱり重要なんですね。

デコード部分

L1キャッシュは64KBに倍増ししている他、Intelとしては初めて、命令キャッシュと一緒に格納されるプレデコード情報を生成する「オンデマンドの命令長デコーダ」を採用します。また、5000エントリにもなる分岐ターゲットキャッシュを搭載しており、より正確な分岐予測も可能です。

1クロックサイクルで最大6命令をデコードすることが可能なOut-Of-Order(OOO)デコーダも採用されています。

実行部分

実行部分では、5ワイドアロケーション、256つのエントリに対応するOOOウィンドウ、そして17ポートの実行ポートを備えています。同社は整数計算においてSkylakeよりもIPCの(クロックあたりの命令実行数)が高く消費電力が抑えられているとしています。

17ポートの実行ユニットからつながる実行エンジンについて。実行エンジンには、4基の整数ALU(演算ユニット)、2基のLoad AGU(アドレス計算ユニット*1)、2基のStore AGU、2基のジャンプポート、2基の整数ストアデータ、2基のFP/ベクトルのAPUと、追加のALUが搭載されています。

キャッシュ&メモリ

最後にメモリサブシステムですが、32KBのデータキャッシュが搭載されており、前述の通りStoreとLoadが2基ずつのAGUが搭載されています。

そして、最大2MBの4コアが共有するL2キャッシュが搭載されています。

命令セット

そして新たにセキュリティのため多層防御を許可するための「Intel Control-flow Enforcement Technology」、仮想技術のリダイレクト保護「Intel VT-rp」などの命令セットの追加がされているほか、256bitのAVXのサポートも含まれています。

これはGracemontの話ですよ。AVXのサポートはアツい。

Golden Cove

そして、Core系統で、Rocket Lakeの「Cypress Cove」とTiger Lakeの「Willow Cove」の正当な後継にあたる「Golden Cove」が性能コアに採用されます。正確には、Willow Coveの後継に当たるといったほうがいいかもしれません。

Core系統のCPUの目標は「CPUアーキテクチャのパフォーマンスをステップアップさせる」とともに「ラップトップからデスクトップ、データセンターまで、あらゆる用途に対応するスケーラブルなアーキテクチャ」としています。

Golden Coveは「低レイテンシ、高シングルスレッド」を実現することを焦点にしているとのこと。

デコード

デコーダのデータ帳は32B長になり、デコーダの数は6基になるなど、大きく向上しています。

OOOエンジンは、6アロケーションと12の実行ポートが搭載。

実行

実行部については、ALUやFADD(加算命令)が追加されており、FMA(積和演算)を利用したFP16の処理にも対応しています。特に、FMAによるFP16の演算は、AVX512命令を実行するときに効率よく演算する事が可能になります。

キャッシュ

キャッチュは、データロードユニットが3ポートにふえ、3x256bitまたは2x512bitのロードが新たに可能になりました。

また、ロードバッファ、ストアバッファも強化されており、メモリからの読み込みをより並列処理する事ができるようになっているとのこと。

L1/L2のキャッシュ容量は変わらずコアあたり1.25MBとなっています。ただし、Sapphire Rapidsに向けて採用される「Golden Cove」はCPUあたり2MBのL2キャッシュを搭載します。

AIのためのAMX

Golden Coveには、Sapphire Rapids向けの機能として、よりAIを効率よく実行するための命令セット「AMX(Advanced Matrix Extensions)」に対応しており、ハード的にAMXの演算ユニットが追加されています。これは、VNNIのなどの延長となる拡張命令セットとなっています。

AMXを使えば、INT8なら2000、Bfloat1なら1000の処理を1クロックサイクルで行うことができます。

コアについてまとめ

Intelは、Golden Coveを採用したAlder Lakeについて、全世代のRocket Lakeと比較して同じクロックで19%の性能が向上するとしています。

第12世代Core「Alder Lake」は今年後半に登場する見込みです。

関連リンク

*1:CPUがメインメモリにアクセスするために使用するアドレスを計算するユニット