ルネサスエレクトロニクス株式会社は、RISC-V ISAをベースとした32bit CPUコアを独自開発したことを発表しました。

汎用的で多様

最近、急速にその開発が進んでいるRISC-Vですが、現状はまだ発展途上の状態にあります。しかしながら、採用例も徐々に登場してきており、ルネサスもAndes TechnologyのRISC-V IPを利用した32bit 音声制御用ASSPと、モータ制御用ASSP、64bit汎用マイクロプロセッサ「RZ/Five」を発売しています。

今回発表されたアーキテクチャは、同社初のオリジナルデザインとなるRISC-Vのコアになっています。

具体的な内容

具体的な設計については、同社でPrincipal Product Marketing Engineerを務めるGiancarlo Parodi氏が書いたブログにてまとめられています。

記事によると、今回発表されたCPUは高いフレキシビリティを有しており、様々なアプリケーションに適応できるとのこと。マイコンのメインCPUから、SoCに内蔵するサブコントローラ、特定用途向けの汎用製品(ASSP)のコアとして採用することを例に上げています。

そして、コア自体が省スペースで設計されていることから、コストへの影響が小さいというメリットがあり、動作電流とスタンバイ時のリーク電流も低減しているとのこと。製品としては小型の組み込みシステムをターゲットにしつつ、高い演算性能を実現しているとしています。

アーキテクチャとしては、RV32/IまたはRV32/Eを選択し、用途によって利用可能な汎用レジスタの数を最適化する事が可能となっています。RISC-Vの命令に加えて、拡張も用意されており、乗算と除算を高速化・最適化したM extension、RTOSベースシステムで並行処理や吐いたアクセス管理の基盤として役立つA extension、16bitのみでエンコードされる圧縮命令のC extension、ビット操作のために用意された命令セットB extensionが例として挙げられています。

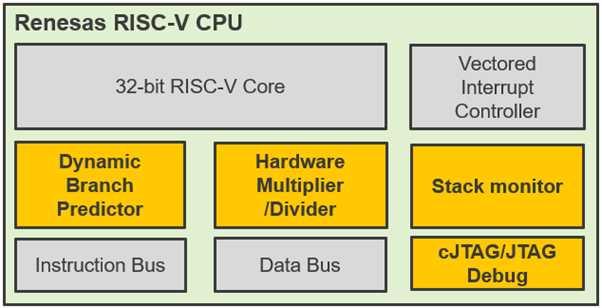

そして、商用向けだなぁっと思った部分ですが、スタックメモリオーバーフローを検出し防止する役割があるスタックモニタレジスタや、投機実行の予測に用いられる動的分岐予測ユニット、デバッグやベンチマークに用いることができるパフォーマンスモニタレジスタが搭載されています。これらのユニットやレジスタによって、信頼性を高めたり、デバッグを容易にしたり、性能の底上げを測ることができそうです。

性能については、先述の独自拡張をあわせて、市場で入手可能な同種のアーキテクチャを凌ぐ、3.27という優れたCoreMark/MHzスコアを達成しているとしています。

同社は、今回発表された自社開発のコアによって急成長中のRISC-V市場のリーダとしての地位を確固たるものにする考えを示しています。